## RIFFA 2.2.2 Documentation

Dustin Richmond, Matt Jacobsen

Thursday 11<sup>th</sup> August, 2016

## Contents

| 1 | Intr | roduction: RIFFA 3                       |

|---|------|------------------------------------------|

|   | 1.1  | What is RIFFA                            |

|   | 1.2  | Licensing 4                              |

| 2 | Get  | tting Started 5                          |

|   | 2.1  | Development Board Support in RIFFA 2.2.2 |

|   | 2.2  | Understanding this User Guide            |

|   | 2.3  | Decoding What's Provided                 |

|   | 2.4  | Release Notes                            |

|   |      | 2.4.1 Version 2.2.2                      |

|   |      | 2.4.2 Version 2.2.1                      |

|   |      | 2.4.3 Version 2.2.0                      |

|   |      | 2.4.4 Version 2.1.0                      |

|   |      | 2.4.5 Version 2.0.2                      |

|   |      | 2.4.6 Version 2.0.1                      |

|   | 2.5  | Errata                                   |

|   |      | 2.5.1 Windows                            |

|   |      | 2.5.2 Linux                              |

|   |      | 2.5.3 Altera                             |

|   |      | 2.5.4 Xilinx (Classic)                   |

|   |      | 2.5.5 Xilinx (Ultrascale)                |

| 3 | Inst | talling the RIFFA driver 12              |

|   | 3.1  | Linux                                    |

|   | 3.2  | Windows                                  |

| 4                                                                        | Cor                                              | npiling                                                                          | g and using the Xilinx Example Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|                                                                          | 4.1                                              | Classi                                                                           | c - 7 Series Integrated Block for PCI Express - (VC707, ZC706 and older)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14 |  |  |  |  |

|                                                                          |                                                  | 4.1.1                                                                            | VC707 and ZC706 Example Designs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14 |  |  |  |  |

|                                                                          |                                                  | 4.1.2                                                                            | Generating the 7 Series Integrated Block for PCI Express $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |  |  |  |  |

|                                                                          |                                                  | 4.1.3 Creating Constraints files for the VC707 Development Board $\ldots \ldots$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|                                                                          |                                                  | 4.1.4                                                                            | Creating Constraints files for the ZC706 Development Board $\ \ldots \ \ldots \ \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 |  |  |  |  |

|                                                                          | 4.2                                              | Ultras                                                                           | cale - Gen3 Integrated Block for PCI Express - (VC709 and newer) $\ \ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22 |  |  |  |  |

|                                                                          |                                                  | 4.2.1                                                                            | VC709 Example Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22 |  |  |  |  |

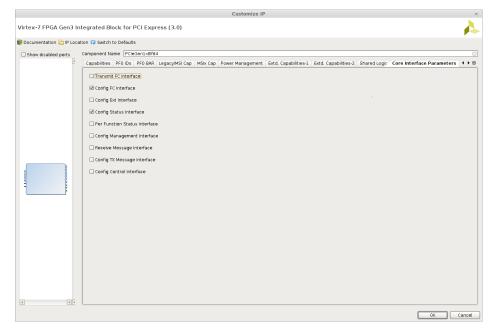

|                                                                          |                                                  | 4.2.2                                                                            | Generating the Gen3 Integrated Block for PCI Express                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22 |  |  |  |  |

|                                                                          |                                                  | 4.2.3                                                                            | Creating Constraints files for the VC709 Development Board $\ . \ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |  |  |  |  |

| <b>5</b>                                                                 | 5 Compiling and using the Altera Example Designs |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

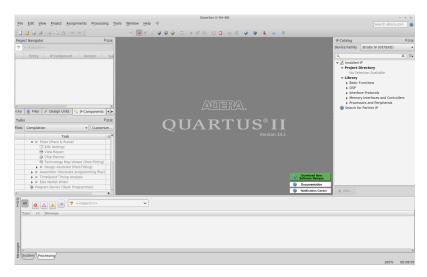

| 5.1 Example Designs with Qsys and MegaWizard (Stratix V, Cyclone V and n |                                                  |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

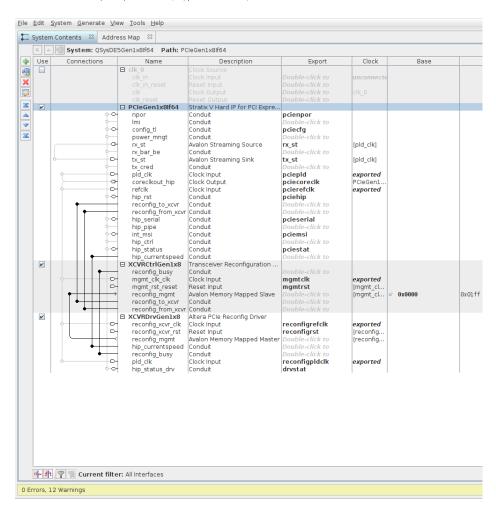

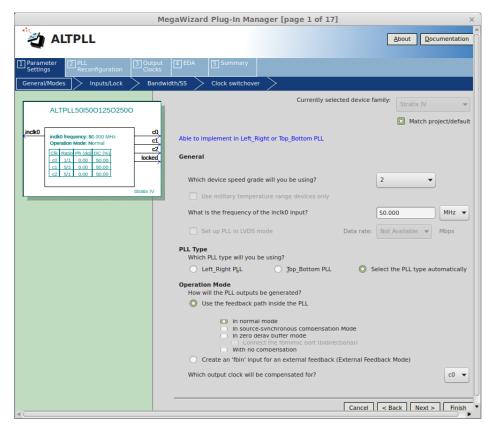

|                                                                          |                                                  | 5.1.1                                                                            | Qsys (Stratix V and newer) $\hdots \hdots \$ | 29 |  |  |  |  |

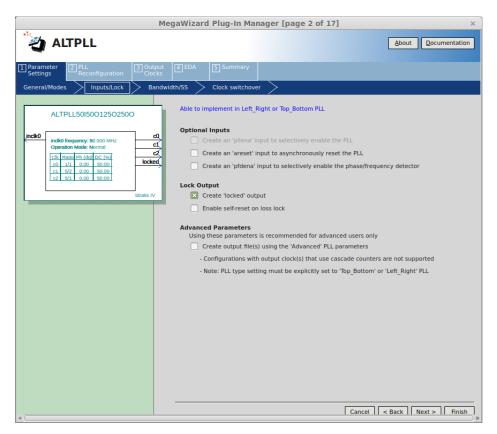

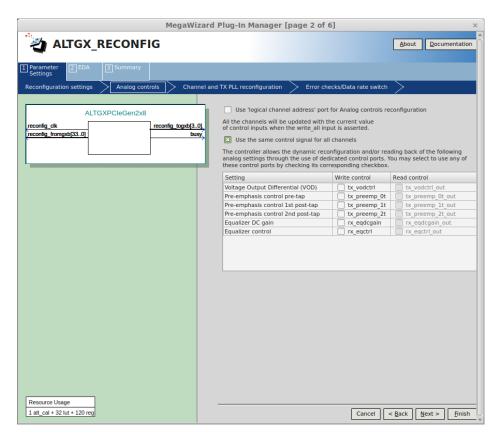

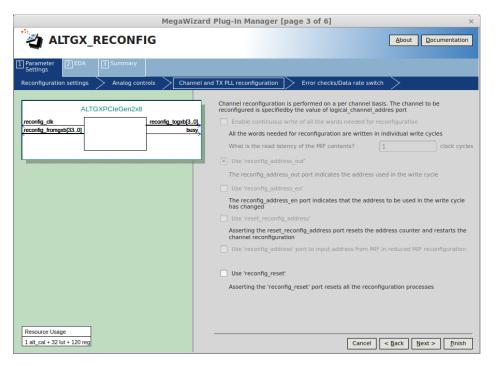

|                                                                          |                                                  | 5.1.2                                                                            | Generating IP using MegaWizard (Stratix V, Cyclone V and newer) $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30 |  |  |  |  |

|                                                                          |                                                  | 5.1.3                                                                            | Creating Constraints files for MegaWizard and QSys Designs $\ . \ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |  |  |  |  |

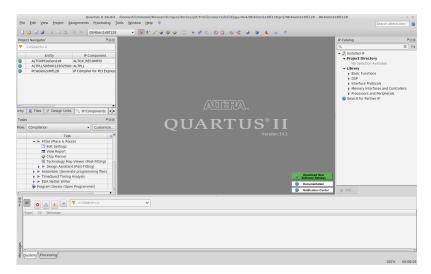

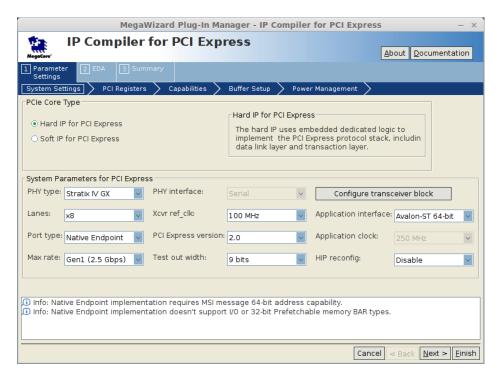

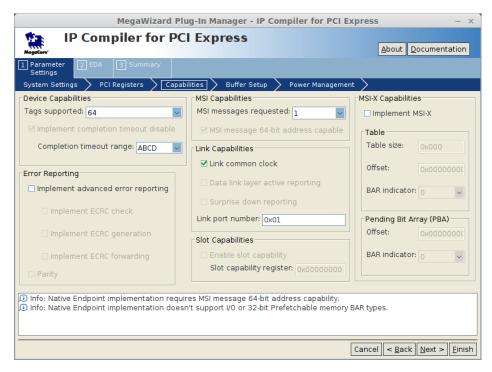

|                                                                          | 5.2                                              | IP Co                                                                            | mpiler for PCI Express (Stratix IV, and older)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39 |  |  |  |  |

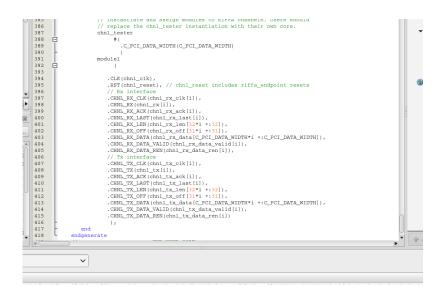

|                                                                          |                                                  | 5.2.1                                                                            | Generating IP with IP Compiler for PCI Express (Stratix IV, and older)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39 |  |  |  |  |

|                                                                          |                                                  | 5.2.2                                                                            | Creating Constraints files for IP Compiler Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49 |  |  |  |  |

| 6                                                                        | Dev                                              | veloper                                                                          | Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |  |  |  |  |

|                                                                          | 6.1 Architecture Description                     |                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |

|                                                                          |                                                  | 6.1.1                                                                            | Scatter Gather DMA Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54 |  |  |  |  |

|                                                                          |                                                  | 6.1.2                                                                            | Data Abstraction DMA Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |  |  |  |  |

|                                                                          | 6.2                                              | Softwa                                                                           | are Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54 |  |  |  |  |

|                                                                          | 6.3                                              | FPGA                                                                             | RX Transfer / Host Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |  |  |  |  |

|                                                                          | 6.4                                              | TX Ti                                                                            | ansfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |  |  |  |  |

|                                                                          | 6.5                                              | FPGA                                                                             | RX Transfer / Host Send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |  |  |  |  |

## 1 Introduction: RIFFA

## 1.1 What is RIFFA

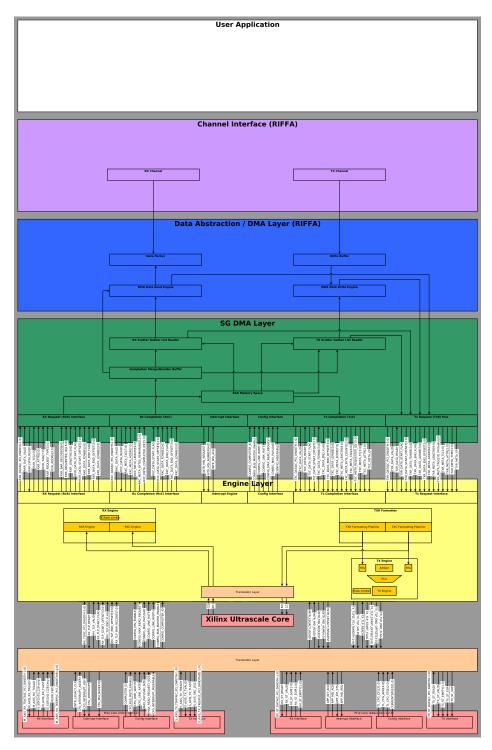

RIFFA (Reusable Integration Framework for FPGA Accelerators) is a simple framework for communicating data from a host CPU to a FPGA via a PCI Express bus. The framework requires a PCIe enabled workstation and a FPGA on a board with a PCIe connector. RIFFA supports Windows and Linux, Altera and Xilinx, with bindings in C/C++, Python, MATLAB and Java.

On the software side there are two main functions: data send and data receive. These functions are exposed via user libraries in C/C++, Python, MATLAB, and Java. The driver supports multiple FPGAs (up to 5) per system. The software bindings work on Linux and Windows operating systems. Users can communicate with FPGA IP cores by writing only a few lines of code.

On the hardware side, users access an interface with independent transmit and receive signals. The signals provide transaction handshaking and a first word fall through FIFO interface for reading/writing data to the host. No knowledge of bus addresses, buffer sizes, or PCIe packet formats is required. Simply send data on a FIFO interface and receive data on a FIFO interface. RIFFA does not rely on a PCIe Bridge and therefore is not subject to the limitations of a bridge implementation. Instead, RIFFA works directly with the PCIe Endpoint and can run fast enough to saturate the PCIe link.

RIFFA communicates data using direct memory access (DMA) transfers and interrupt signaling. This achieves high bandwidth over the PCIe link. In our tests we are able to saturate (or near saturate) the link in all our tests. The RIFFA distribution contains examples and guides for setting up designs on several standard development boards.

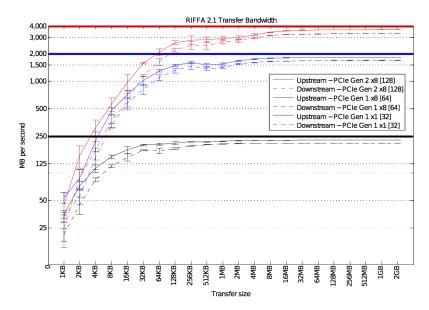

Figure 1.1: Graph of Bandwidth vs Transfer Size

RIFFA 2.2.2 is significantly more efficient than its predecesor RIFFA 1.0. RIFFA 2.2.2 is able to saturate the PCIe link for nearly all link configurations supported. Figure 1.1 shows the performance of designs using the 32 bit, 64 bit, and 128 bit interfaces. The colored bands show the bandwidth region between the theoretical maximum and the maximum achievable. PCIe Gen 1 and 2 use 8 bit / 10 bit encoding which limits the maximum achievable bandwidth to 80% of the theoretical. Our experiments show that RIFFA can achieve 80% of the theoretical bandwidth in nearly all cases. The 128 bit interface achieves 76% of the theoretical maximum.

If you are using RIFFA on a new platform not listed above let us know and well help you out!

## 1.2 Licensing

Copyright (c) 2016, The Regents of the University of California All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- Neither the name of The Regents of the University of California nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIM-ITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL REGENTS OF THE UNIVERSITY OF CALIFORNIA BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDEN-TAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (IN-CLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## 2 Getting Started

## 2.1 Development Board Support in RIFFA 2.2.2

RIFFA 2.2.2 supports:

- The VC707, ZC706 and similar boards with the Xilinx IP Core 7-Series Integrated Block for PCI Express. Example designs for the VC707 and ZC706 boards are provided, and contain this core. The current distribution supports all 64-bit interfaces for these devices, with 128-bit support coming soon after the initial release. (Support for the 128-bit interface is in RIFFA 2.1, but is temporarily mising due to changes)

- The VC709 board and similar boards with the Xilinx IP Gen3 Integrated Block for PCI Express. Example designs for the VC709 are provided, and contain this core. The current distribution supports all 64-bit and 128-bit AXI interfaces. 256-bit (PCIe Gen3 x8) support is planned for a later date.

- The DE5-Net board and similar boards with the Stratix V, Cyclone V, and Arria V, Hard IP for PCI express (Avalon Streaming Interface). Example designs for the DE5-net board are provided, and contain the Stratix V version of this core. The current distribution supports all 64-bit and 128-bit Avalon Streaming interfaces.

- The DE4 and similar boards with the IP Compiler for PCI Express Core, supporting Stratix IV, Cyclone IV and Arria II devices. Example designs for the DE4 board are provided. The current distribution supports all 64-bit and 128-bit Avalon Streaming interfaces.

## 2.2 Understanding this User Guide

In this user guide, we use the following conventions:

| Object                         | Example                            |

|--------------------------------|------------------------------------|

| Directories and Paths          | RIFFA 2.2.2/source/fpga/riffa      |

| Xilinx Specific Content        | vc709                              |

| Altera Specific Content        | de5                                |

| Configuration Setting          | Number of Lanes                    |

| Terminal Command, Code Snippet | <pre>\$ echo ''Hello World''</pre> |

| RIFFA Parameter                | $C_{-}NUM_{-}CHNL$                 |

## 2.3 Decoding What's Provided

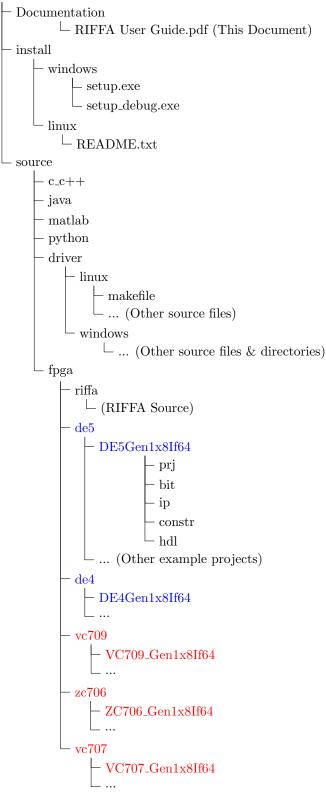

Fig 2.1 shows the directory hierarchy of RIFFA. This instruction manual uses this directory tree when specifying all directory paths.

The *RIFFA 2.2.2/source/fpga/* contains a directory for each board we have tested for the current distribution:de5, de4, VC709, VC707, ZC706. Each board directory has several example project directories (e.g. DE5Gen1x8If64 and VC709\_Gen1x8If64). Each example project directory has 5 sub-directories:

• *prj*/ contains all of the project files (.qsf,.qpf, .xpr).

- *ip*/ contains all of the ip files (.qsys, .xci) generated for the project, when permitted by licensing agreements.

- *bit/* contains the example programming file for the corresponding FPGA example design. Quartus and Vivado do not modify this programming (.sof, .bit).

- *constr/* contains the user constraint files (.sdc, .xdc).

- hdl/ contains any example-project specific Verilog files, such as the project top level file.

## RIFFA 2.2.2

Figure 2.1: Directory hierarchy of the RIFFA 2.2.2 distribution

## 2.4 Release Notes

## 2.4.1 Version 2.2.2

- Fixed: Unsigned Windows Driver (Commit: 4e989fc)

- Fixed: A bug in the clock-crossing interface where a low-frequency user clock (j40 MHz) could cause incorrect channel behavior. (Commit: 778c42e)

- Fixed: Support for 64-bit pointers in Python 3. Shout out to @jrobrien (Commit: af7c592)

- Fixed: Includes in linux driver. linux/slab.h was not included in riffa\_driver.c (Commit: cd494e1)

- Fixed: Capability backwards/forwards compatibility issues to support Linux for Tegra. (Commit: 1d228c1)

- New: Support for new get\_user\_pages API in the linux kernel. Shout out to @marzoul (Commit: TBD)

- Removed: Non-Qsys DE5 Board Example Designs (QSys ¿ IP Generator) @marzoul (Commit: TBD)

## 2.4.2 Version 2.2.1

- New: Reset logic for the Engine layer to handle RIFFA induced resets

- New: Stability/multi-thread-concurrency warnings in the Linux driver (Shoutout to @marzoul)

- Fixed: A bug in the Linux Driver that prevented compilation on older kernels

- Fixed: Windows driver issue for back-to-back small transfers (See 2.2.0)

- Fixed: WORD\_ENABLE bug fix for the Classic Xilinx (VC707, ZC706, AC701, KC705) 128-bit interface

- Fixed: TX Engine Buffer sizing (high-bandwidth transfers occasionally had corruption)

- Fixed: RX Engine rx\_st\_valid bug fix for Altera IP Compiler for PCI express (Cyclone IV, Stratix IV)

## 2.4.3 Version 2.2.0

- Added: Support for the new Gen3 Integrated Block for PCIe Express, and the VC709 Development board.

- Added: ZC706 Example Designs

- Changed: Xilinx example project packaging. All Xilinx Virtex 7 projects are now click-tocompile, and come with instantiated IP.

- Re-wrote and refactored: Various parts of the TX and RX engines to maximize code reuse between different vendors and PCIe endpoint implementations

- Fixed: A bug in the Linux Driver that prevented compilation on older kernels

- Fixed: A bug in the Windows Driver that prevented repeated small transfers.

## 2.4.4 Version 2.1.0

- Added reorder\_queue and updated many rx/tx engine and channel modules that use it.

- Added parameters for number of tags to use and max payload length for sizing RAM for reorder\_queue.

- Fixed: Bug in the riffa\_driver.c, too few circular buffer elements.

- Fixed: Bug in the riffa\_driver.c, bad order in which interrupt vector bits were processed. Can cause deadlock in heavy use situations.

- Fixed: Bug in the tx\_port\_writer.v, maxlen did not start with a value of 1. Can cause deadlock behavior on second transfer.

- Fixed: Bug in the rx\_port\_reader.v, added delay to allow FIFO flush to propagate.

- Fixed: Bug in rx\_port\_xxx.v, changed to use FWFT FIFO instead of existing logic that could cause CHNL\_RX\_DATA\_VALID to drop for a cycle after CHNL\_RX dropped even when there is still data in the FIFO. Can cause premature transmission termination.

- Changed rx\_port\_channel\_gate.v to use FWFT FIFO.

- Removed unused signal from rx\_port\_requester\_mux.v.

- Fixed: Typo/bug that would attempt to change state within tx\_port\_monitor\_xxx.v.

- Added flow control for receive credits to avoid over driving upstream transactions (applies to Altera devices).

## 2.4.5 Version 2.0.2

- Fixed: Bug in Windows and Linux drivers that could report data sent/received before such data was confirmed.

- Fixed: Updated common functions to avoid assigning input values.

- Fixed: FIFO overflow error causing data corruption in tx\_engine\_upper and breaking the Xilinx Endpoint.

- Fixed: Missing default cases in rx\_port\_reader, sg\_list\_requester, tx\_engine\_upper, and tx\_port\_writer.

- Fixed: Bug in tx\_engine\_lower\_128 corrupting s\_axis\_tx\_tkeep, causing Xilinx PCIe endpoint core to shut down.

- Fixed: Bug in tx\_engine\_upper\_128 causing incomplete TX data timeouts.

- Changed rx\_engine to not block on nonposted TLPs. They're added to a FIFO and serviced in order.

- Reset rx\_port FIFOs before a receive transaction to avoid data corruption from replayed TLPs.

## 2.4.6 Version 2.0.1

- RIFFA 2.0.1 is a general release. This means we've tested it in a number of ways. Please let us know if you encounter a bug.

- Neither the HDL nor the drivers from RIFFA 2.0.1 are backwards compatible with the components of any previous release of RIFFA.

- RIFFA 2.0.1 consumes more resources than 2.0 beta. This is because 2.0.1 was rewritten to support scatter gather DMA, higher bandwidth, and appreciably more signal registering. The additional registering was included to help meet timing constraints.

- The Windows driver is supported on Windows 7 32/64. Other Windows versions can be supported. The driver simply needs to be built for that target.

- Debugging on Windows is difficult because there exists no system log file. Driver log messages are visible only to an attached kernel debugger. So to see any messages you'll need the Windows Development Kit debugger (WinDbg) or a small utility called DbgView. DbgView is a standalone kernel debug viewer that

- http://technet.microsoft.com/ens/sysinternals/bb896647.aspx Run DbgView with administrator privileges and be sure to enable the following capture options: Capture Kernel, Capture Events, and Capture Verbose Kernel Output.

- The Linux driver is supported on kernel version 2.6.27+.

- The Java bindings make use of a native library (in order to connect Java JNI to the native library). Libraries for Linux and Windows for both 32/64 bit platforms have been compiled and included in the riffa.jar.

- Removed the CHNL\_RX\_ERR signal from the channel interface. Error handling now ends the transaction gracefully. Errors can be easily detected by comparing the number of words received to the CHNL\_RX\_LEN amount. An error will cause CHNL\_RX will go low prematurely and not provide the advertised amount of data.

- Fixed: Bug in sg\_list\_requester which could cause an unbounded TLP request.

- Fixed: Bug in tx\_port\_buffer\_128 which could stall the TX transaction.

## 2.5 Errata

While we have extensively tested the current distribution, we are human and cannot eliminate all bugs in our distribution. As a general rule of thumb, if you find yourself delving into the RIFFA code, you have gone too far. Contact us if you need additional assistance!

See the following notes for issues we are currently tracking:

## 2.5.1 Windows

## 2.5.2 Linux

No open issues

#### 2.5.3 Altera

Issue 3: No support for the 256-bit, Gen3x8 Interface Coming soon...

#### 2.5.4 Xilinx (Classic)

**Issue 1: Missing example designs for ML605** There is no disadvantage to using RIFFA 2.1.0 until we return support in a future distribution.

Issue 2: Missing example design for Spartan 6 LXT Development board The 32-bit interface support has been removed from RIFFA 2.2 and may be added back in the future. Please use RIFFA 2.1 in the meantime

## 2.5.5 Xilinx (Ultrascale)

Issue 1: No support for the 256-bit, Gen3x8 Interface Coming soon...

## 3 Installing the RIFFA driver

## 3.1 Linux

To install the RIFFA driver in linux, you must build it against your installed version of the Linux kernel. RIFFA 2.2.2 comes with a makefile that will install the necessar linux kernel headers and the driver. This makefile will also build and install the C/C++ native library. To install RIFFA 2.2.2 in linux, follow these instructions:

- 1. Open a terminal in linux and navigate to the RIFFA 2.2.2/source/driver/linux directory.

- 2. Ensure you have the kernel headers installed, run:

#### \$ sudo make setup

This will attempt to install the kernel headers using your system's package manager. You can skip this step if you've already installed the kernel headers.

3. Compile the driver and C/C++ library:

\$ make

$\operatorname{or}$

#### \$ make debug

Using make debug will compile in code to output debug messages to the system log at runtime. These messages are useful when developing your design. However they pollute your system log and incur some overhead. So you may want to install the non-debug version after you've completed development.

4. Install the driver and library:

#### \$ sudo make install

The system will be configured to load the driver at boot time. The C/C++ library will be installed in the default library path. The header files will be placed in the default include path. You will need to reboot after you've installed for the driver to be (re)loaded.

- 5. If the driver is installed and there is a RIFFA 2.2.2 configured FPGA when the computer boots, the driver will detect it. Output in the system log will provide additional information.

- 6. The C/C++ code must include the riffa.h header. An example inclusion is shown in Listing 3.1

- 7. When compiling (using GCC/G++, etc.) you must link with the RIFFA libraries using the -lriffa flag. For example, when compiling test.c from Listing 3.1:

\$ gcc -g -c -lriffa -o test.o test.c

8. Bindings for other languages can be installed by following the README files in their respective directories (See Figure 2.1

## 3.2 Windows

Currently only Windows 7 (32/64) is supported by RIFFA 2.2.2. In the RIFFA 2.2.2/install/windows/ subdirectory use the provided setup.exe program to install the RIFFA driver and native C/C++ library. You can verify that RIFFA 2.2.2 installed correctly by checking the installation directory in Program Files. After installation, you'll be able to install the bindings for other languages.

The setup\_dbg.exe installer installs a driver with additional debugging output. You can install the setup\_dbg.exe version and then later use setup.exe to install the non-debug output version.

Listing 3.1: Inclusion of the RIFFA header files in a user application

```

#include <stdio.h>

#include <stdio.h>

#include <stdlib.h>

#include <riffa.h>

#define BUF_SIZE (1*1024*1024)

unsigned int buf[BUF_SIZE];

int main(int argc, char* argv[]) {

fpga_t * fpga;

int fid = 0; // FPGA id

int channel = 0; // FPGA channel

fpga = fpga_open(fid);

fpga_recv(fpga, channel, (void *)buf, BUF_SIZE, 0, 1, 0);

fpga_close(fpga);

return 0;

}

```

## 4 Compiling and using the Xilinx Example Designs

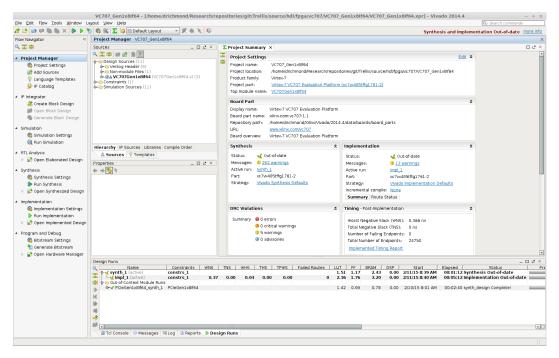

Vivado 2014.4 was used in all example designs and documentation included in this distribution. We highly recommend using 2014.4 and all newer versions of the software, since we have encountered bugs in previous versions of the Vivado (e.g. 2014.2) software. This guide assumes that the end-user has already configured their board for PCI Express operation. See the VC709 User Guide <sup>1</sup>, VC707 User Guide <sup>2</sup> or ZC706 User Guide <sup>3</sup>.

While we have not tested all of the current-generation Xilinx development boards, we are confident that they can be supported with minimal modifications. For more information about supporting new boards, see the sections 4.1.2 and 4.2.2. These sections cover the settings used in the RIFFA example design IP.